1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

| MIPS Instruction Set Architecture

---------------------<reserved registers>------------------------

$0 zero

$1 assembler temporary

$29 stack pointer

$31 return address

---------------------<R-type Instructions>-----------------------

ADDU $rd,$rs,$rt R[rd] <= R[rs] + R[rt] (unchecked overflow)

ADD $rd,$rs,$rt R[rd] <= R[rs] + R[rt]

AND $rd,$rs,$rt R[rd] <= R[rs] AND R[rt]

JR $rs PC <= R[rs]

NOR $rd,$rs,$rt R[rd] <= ~(R[rs] OR R[rt])

OR $rd,$rs,$rt R[rd] <= R[rs] OR R[rt]

SLT $rd,$rs,$rt R[rd] <= (R[rs] < R[rt]) ? 1 : 0

SLTU $rd,$rs,$rt R[rd] <= (R[rs] < R[rt]) ? 1 : 0

SLLV $rd,$rs,$rt R[rd] <= R[rt] << [0:4] R[rs]

SRLV $rd,$rs,$rt R[rd] <= R[rt] >> [0:4] R[rs]

SUBU $rd,$rs,$rt R[rd] <= R[rs] - R[rt] (unchecked overflow)

SUB $rd,$rs,$rt R[rd] <= R[rs] - R[rt]

XOR $rd,$rs,$rt R[rd] <= R[rs] XOR R[rt]

---------------------<I-type Instructions>-----------------------

ADDIU $rt,$rs,imm R[rt] <= R[rs] + SignExtImm (unchecked overflow)

ADDI $rt,$rs,imm R[rt] <= R[rs] + SignExtImm

ANDI $rt,$rs,imm R[rt] <= R[rs] & ZeroExtImm

BEQ $rs,$rt,label PC <= (R[rs] == R[rt]) ? npc+BranchAddr : npc

BNE $rs,$rt,label PC <= (R[rs] != R[rt]) ? npc+BranchAddr : npc

LUI $rt,imm R[rt] <= {imm,16b'0}

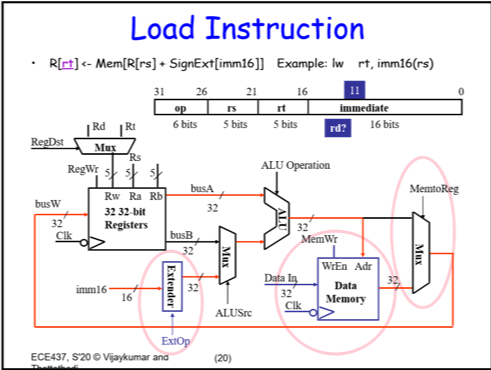

LW $rt,imm($rs) R[rt] <= M[R[rs] + SignExtImm]

ORI $rt,$rs,imm R[rt] <= R[rs] OR ZeroExtImm

SLTI $rt,$rs,imm R[rt] <= (R[rs] < SignExtImm) ? 1 : 0

SLTIU $rt,$rs,imm R[rt] <= (R[rs] < SignExtImm) ? 1 : 0

SW $rt,imm($rs) M[R[rs] + SignExtImm] <= R[rt]

LL $rt,imm($rs) R[rt] <= M[R[rs] + SignExtImm]; rmwstate <= addr

SC $rt,imm($rs) if (rmw) M[R[rs] + SignExtImm] <= R[rt], R[rt] <= 1 else R[rt] <= 0

XORI $rt,$rs,imm R[rt] <= R[rs] XOR ZeroExtImm

---------------------<J-type Instructions>-----------------------

J label PC <= JumpAddr

JAL label R[31] <= npc; PC <= JumpAddr

---------------------<Other Instructions>------------------------

HALT

---------------------<Pseudo Instructions>-----------------------

PUSH $rs $29 <= $29 - 4; Mem[$29+0] <= R[rs] (sub+sw)

POP $rt R[rt] <= Mem[$29+0]; $29 <= $29 + 4 (add+lw)

NOP Nop

-----------------------------------------------------------------

-----------------------------------------------------------------

org Addr Set the base address for the code to follow

chw # Assign value to half word memory

cfw # Assign value to word of memory

|